金予,工学博士,讲师,硕士生导师,分别于2014年和2010年在日本早稻田大学信息、生产和系统研究生院获得博士和硕士学位。主要研究方向为数模混合集成电路设计,高位验证,可测性设计等方面的研究工作。2014年12月起,入职北京化工大学信息科学与技术学院,致力于与嵌入式系统开发的教学与研究。技术上可覆盖数字、模拟集成电路设计,产品需求、原型验证、前端、后端设计流程,流片加工,封装测试等端到端技术,先后主持3项企业合作项目,有力支撑3项国家自然基金项目。在此期间,先后发表了SCI/EI收录论文10余篇,承担《IEEEsensor》,《IEEETrans.on SystemandCircuits》审稿人。加速设计。邮箱:jiny@mail.buct.edu.cn

金予,工学博士,讲师,硕士生导师,分别于2014年和2010年在日本早稻田大学信息、生产和系统研究生院获得博士和硕士学位。主要研究方向为数模混合集成电路设计,高位验证,可测性设计等方面的研究工作。2014年12月起,入职北京化工大学信息科学与技术学院,致力于与嵌入式系统开发的教学与研究。技术上可覆盖数字、模拟集成电路设计,产品需求、原型验证、前端、后端设计流程,流片加工,封装测试等端到端技术,先后主持3项企业合作项目,有力支撑3项国家自然基金项目。在此期间,先后发表了SCI/EI收录论文10余篇,承担《IEEEsensor》,《IEEETrans.on SystemandCircuits》审稿人。加速设计。邮箱:jiny@mail.buct.edu.cn

主要科研项目 Research Projects

项目名称 | 项目来源 |

基于微流控芯片的孔隙尺度微生物采油过程重建与控制机理研究 | 国家自然科学基金(参与) |

空间信息网络下的高光谱遥感协同观测理论与方法研究 | 国家自然科学基金(参与) |

空间信息网络下的高光谱遥感协同观测理论与方法研究 | 企业横向课题 |

企业横向课题 | |

ASIC芯片后端设计与集成测试服务 | 企业横向课题 |

电动特种车上位控制系统技术服务 | 企业横向课题 |

主要论文Research Paper

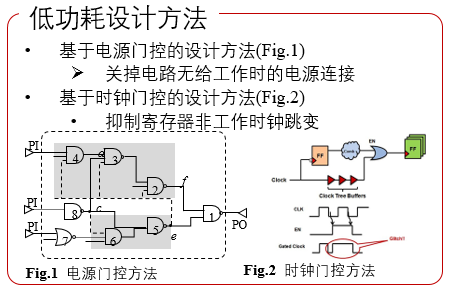

Jin Yu; Kimura Shinji*. On Gate Level Power Optimization of Combinational Circuits Using Pseudo Power Gating[J]. Ieice Transactions on Fundamentals of Electronics Communications & Computer Sciences, 2012, E95.A(12):2191-2198.

in Yu; Du Zhe; Kimura S*. Dual-Stage Pseudo Power Gating with Advanced Clustering Algorithm for Gate Level Power Optimization[J]. Ieice Transactions on Fundamentals of Electronics Communications & Computer Sciences, 2013, E96.A(12):2568-2575.

Wu Jingjing; Jin Yu*;Li Wei;Gao Lianru; Bing Zhang; FPGA implementation of collaborative representation algorithm for real-time hyperspectral target detection[J]. Journal of Real-Time Image Processing, 2018,15:673–685.

Xu Chi; Jin, Yu*; Yu Duli;Wang Xin; A fractional-order zero-phase integrator for sigma-delta modulator, Analog Integrated Circuits and Signal Processing,2019, 00: 335-343.

徐驰; 金予*; 俞度立; 基于高阶Sigma-Delta调制器的PD~α相位补偿器设计,自动化与仪器仪表,2019, 09: 1-3+11.

主要专利 Patent

裴松伟; 张敬东; 金予;三维集成电路中缺陷硅通孔的容错电路,中国,2015-04, ZL201510204655.5

胡晓磊; 金予; 基于PCIE与FPGA结合的多核JTAG调试代理系统, 2019-03, CN208596371U

研究成果Research Achievements